- 您现在的位置:买卖IC网 > Sheet目录3879 > PIC18F4539-E/PT (Microchip Technology)IC PIC MCU FLASH 12KX16 44TQFP

2002 Microchip Technology Inc.

Preliminary

DS30485A-page 111

PIC18FXX39

13.2

Timer3 Interrupt

The TMR3 Register pair (TMR3H:TMR3L) increments

from 0000h to FFFFh and rolls over to 0000h. The

TMR3 Interrupt, if enabled, is generated on overflow,

which is latched in interrupt flag bit, TMR3IF

(PIR2<1>). This interrupt can be enabled/disabled by

setting/clearing TMR3 interrupt enable bit, TMR3IE

(PIE2<1>).

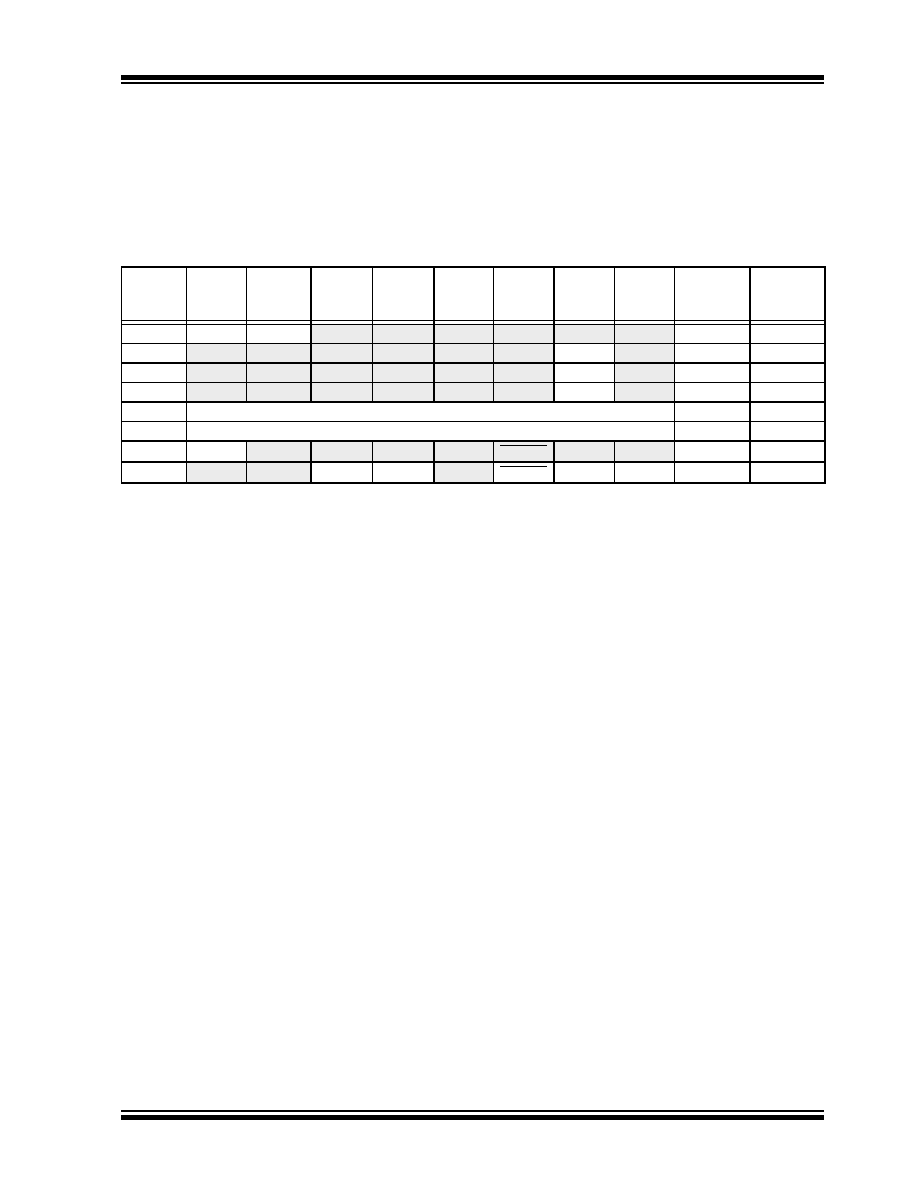

TABLE 13-1:

REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Value on

POR, BOR

Value on

All Other

RESETS

INTCON

GIE/GIEH PEIE/GIEL TMR0IE

INT0IE

RBIE

TMR0IF

INT0IF

RBIF

0000 000x

0000 000u

PIR2

—

EEIF

BCLIF

LVDIF

TMR3IF

—

---0 0000

PIE2

—

EEIE

BCLIE

LVDIE

TMR3IE

—

---0 0000

IPR2

—

EEIP

BCLIP

LVDIP

TMR3IP

—

---1 1111

TMR3L

Holding Register for the Least Significant Byte of the 16-bit TMR3 Register

xxxx xxxx

uuuu uuuu

TMR3H

Holding Register for the Most Significant Byte of the 16-bit TMR3 Register

xxxx xxxx

uuuu uuuu

T1CON

RD16

—

T1CKPS1 T1CKPS0

—

T1SYNC TMR1CS TMR1ON 0-00 0000 u-uu uuuu

T3CON

RD16

—

T3CKPS1 T3CKPS0

—

T3SYNC TMR3CS TMR3ON 0000 0000 uuuu uuuu

Legend:

x

= unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18F8525-E/PT

IC PIC MCU FLASH 24KX16 80TQFP

XF2L-3035-1

CONN FPC 30POS 0.5MM SMT

PIC16F1938-I/SS

IC MCU 8BIT FLASH 28SSOP

PIC16F627A-I/SO

IC MCU FLASH 1KX14 EEPROM 18SOIC

PIC18F65J11-I/PT

IC PIC MCU FLASH 16KX16 64TQFP

PIC18F2439-E/SO

IC PIC MCU FLASH 6KX16 28SOIC

PIC16LF1938-I/SS

IC MCU 8BIT FLASH 28SSOP

PIC16C621A-20/SO

IC MCU OTP 1KX14 COMP 18SOIC

相关代理商/技术参数

PIC18F4539-I/ML

功能描述:8位微控制器 -MCU 24KB 1408 RAM 32 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4539-I/P

功能描述:8位微控制器 -MCU 24KB 1408 RAM 32 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4539-I/P

制造商:Microchip Technology Inc 功能描述:IC 8BIT FLASH MCU 18F4539 DIP40

PIC18F4539-I/PT

功能描述:8位微控制器 -MCU 24KB 1408 RAM 32 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4539IPT

制造商:MICRO CHIP 功能描述:NEW

PIC18F4539T-E/ML

功能描述:8位微控制器 -MCU 24KB 1408 RAM 32 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4539T-E/PT

功能描述:8位微控制器 -MCU 24KB 1408 RAM 32 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4539T-I/ML

功能描述:8位微控制器 -MCU 24KB 1408 RAM 32 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT